首頁 / 最新消息

最新消息

成功實現高速數位設計的 4 個考量, 電源完整性, 信號完整性, PDN

隨著複雜性增加,全方位設計變得更重要

高速數位標準正迅速發展,以因應 5G、物聯網、人工智慧、虛擬實境,以及自動駕駛汽車等新興技術,對高速資料傳輸的需求。每一代高速運算標準的更迭,都帶來新的信令功能、更快的資料傳輸速率,以及更小的設計邊限。然而,隨著速度大幅提升,工程師卻面臨著新的設計挑戰。因此,您需要準確度更高的模擬、新的軟體工具,以及更有效率的工作流程。

身為硬體工程師,您的工作是設計、驗證、製造和測試電子產品。在產業趨勢急速變化的今天,您必須採用全新的設計方法,以解決印刷電路板 (PCB) 高速信號品質下降,甚至於產品故障的問題。其後果可能是專案延遲、預算超支,或商譽嚴重受損等風險。

想要避免這種進退兩難的局面,就需要新的設計工具,以及可連接多個專業領域的全方位設計方法。如此一來,您可根據各種不同的介面標準進行設計,但設計和驗證時間不會因而延長。請閱讀此電子書,了解成功實現完整高速數位設計的 4 個重要考量。

模擬 PCB 信號完整性的最佳時間點,是布局後、製造前。隨著數位設計的速度不斷提高,進行完整的模擬變得越來越重要。而且現在有更多因素,會導致信號完整性問題。經常出現的問題包括:互連裝置的反射(阻抗不匹配)、導線之間的電磁耦合,以及接地問題等。這些問題如不加以解決,可能會導致信號失真和衰減。

從長遠效益來看,進行信號完整性分析和模擬,可減少後期設計失敗的風險,並可協助您將設計邊限最大化,進而節省時間和金錢。

了解實現數位通道信號完整性的 3 個步驟

理想狀況下,從繪製電路圖,到電路板通過最終測試的每個環節,您都應該將信號完整性納入考量。藉由以模擬方式測試您的創新設計,是驗證通道信號完整性的最佳方法。為此,請遵循以下 3 個步驟:

第 1 步:使用眼圖來模擬通道

信號會從發射器穿過 PCB 傳送到接收器。在傳播過程中,導線、連接器和纜線都會產生干擾,信號的振幅和時序將因而惡化。透過眼圖,您可確認信號到達接收器時的品質。

第 2 步:找到導致信號品質惡化的問題根源

發現信號完整性問題後,您可透過 2 項主要分析,來確定數位設計的問題根源。

第 3 步:解決設計問題

找出導致信號完整性問題的根源後,您需考慮可針對設計進行哪些修改。

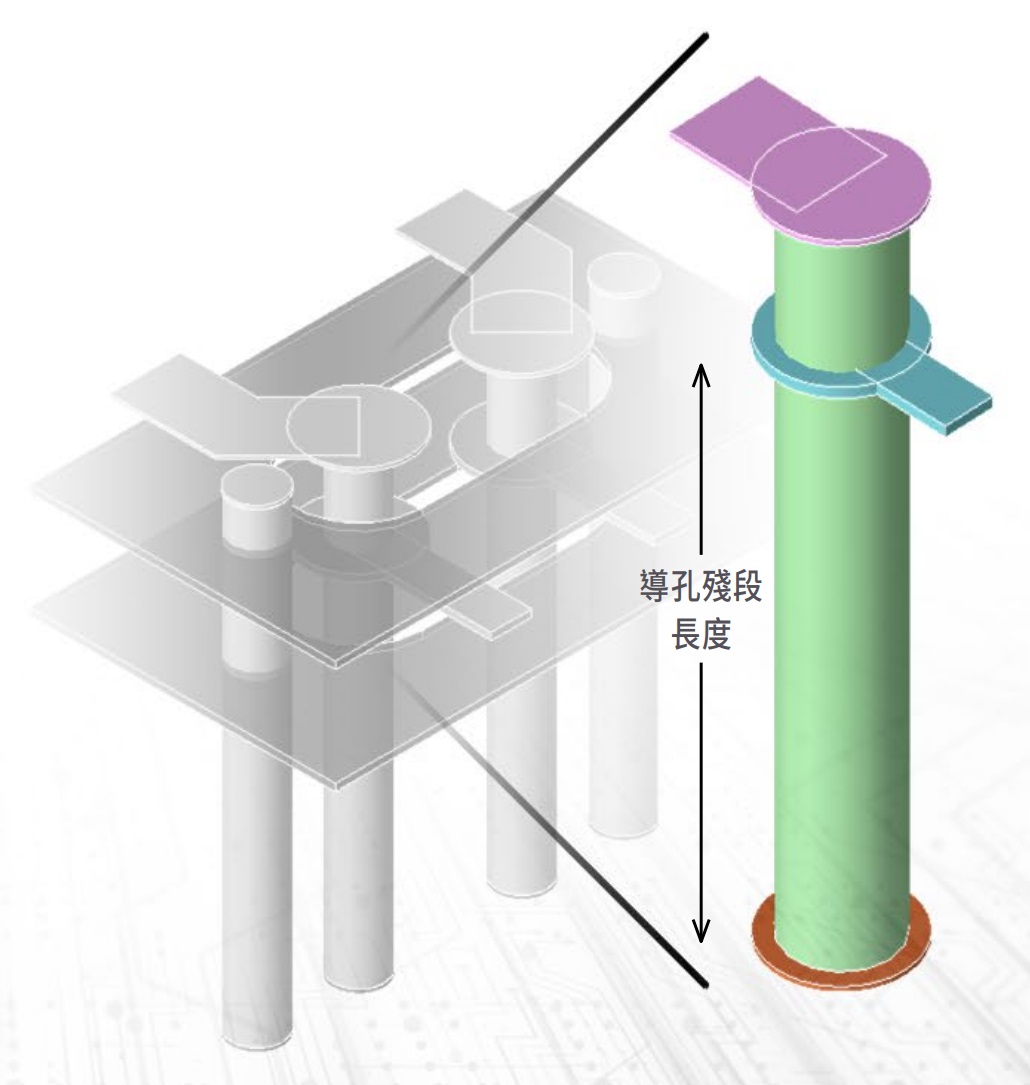

一個常見的問題根源是導孔殘段的長度。導孔可在多個 PCB 層之間提供電子連接,而導孔殘段是連接器中用不到的部分,會導致信號品質顯著下降。進行背鑽(back drilling,亦即使 用鑽頭去除不需要的殘段)有助於大幅改善信號完整性。完成設計修正後,請務必再次模擬通道,確保您的眼圖是張開的。

進行電源完整性分析的目的是,確保電路板上的驅動器和接收器,都能獲得正常運作所需的電壓和電流。為確保電源完整性,您需避免設計出現直流壓降(電流流經電源層與接地層的電阻時所出現的電壓損耗)。

早期了解設計細節至關重要

以下 3 項要求,使得電源完整性挑戰變得更嚴苛,並提高了出現直流壓降的機率。

1. 更高的元件整合度 – 更高的整合度有助於實現更密集的布線,進而提高電源網路的電流密度,但同時也會造成更大的直流壓降。

2. 更低的電源電壓 – 1 V 的 10% 容差度,要比 1.2 V 的 10% 容差度更嚴格,因此會出現更大的壓降。

3. 更小的外觀尺寸 – 隨著 PCB 尺寸變小, 可容納更寬電源平面的空間也變得更小, 進而導致直流壓降。

您不能等到完成布局後,再來執行電源完整性分析。因此,早期了解設計細節,是在高速數位電路板上成功供電的關鍵。

有助於了解電源完整性的 2 項關鍵分析

早期模擬和分析,有助於確保電路板的電源完整性。請務必將這 2 項分析,視為整體高速數位設計流程的一部分。

分析 1:直流壓降

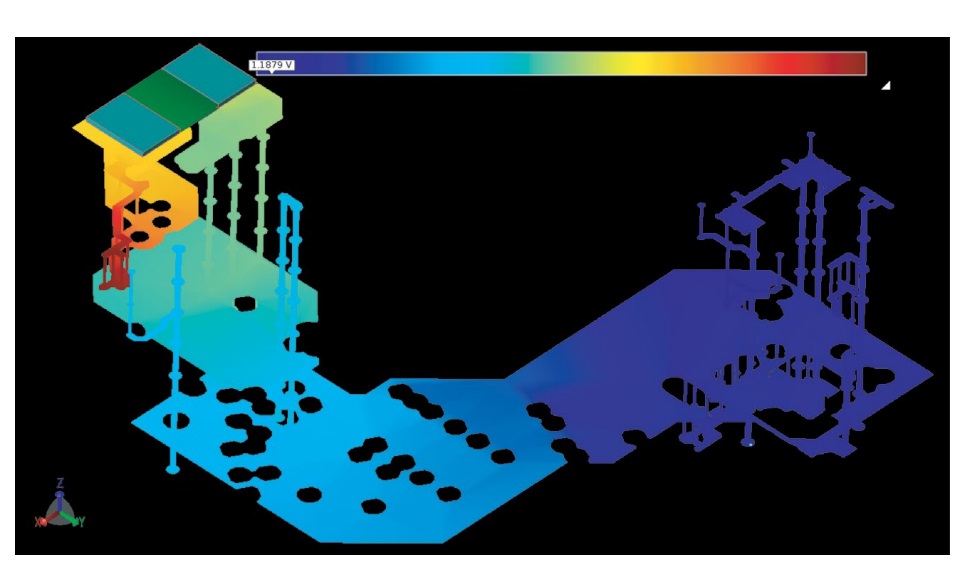

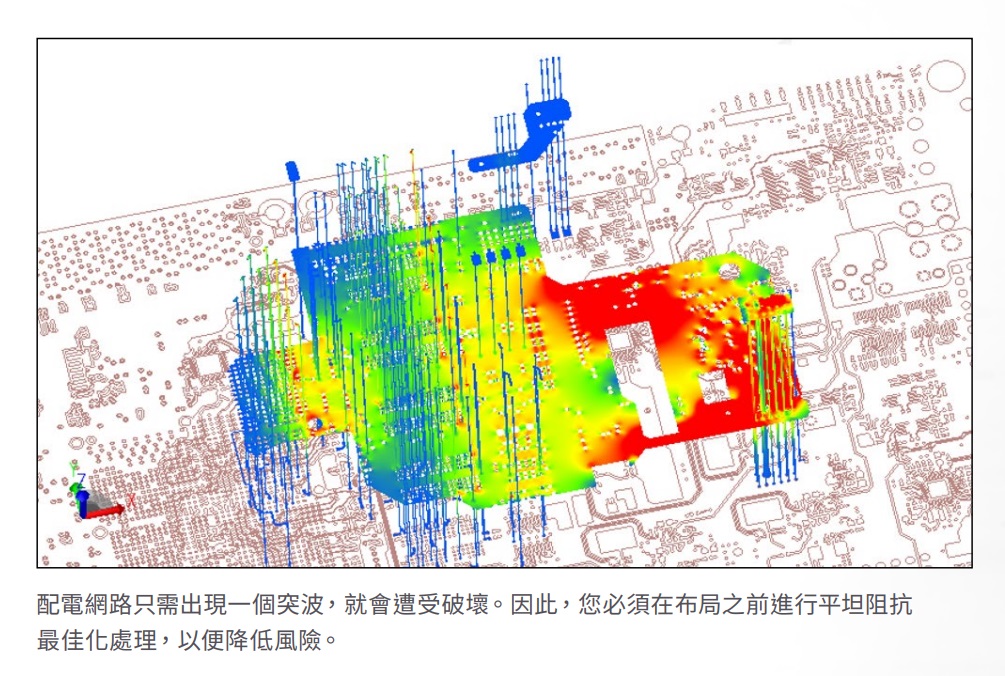

在整個 PCB 上分配電源時,如果 壓降過 大,則負載 端之電 壓可能無法因應必要元件規格的要求。直流壓降分析可確保 PCB 導線和平面,能夠符合電源供應器的要求。

而且這項分析功能,可顯示選定之電源網路和接地網路的電壓分布狀態。您還可利用此分析來檢視電流密度,以了解如何全面改善您的設計。請務必查看電源供應器穩壓器模組及其導孔的位置。此外,您需考慮電流被迫流經導孔周圍孔洞 (void) 之狹窄路徑的問題。

分析 2:交流阻抗

您必須同時從直流 (DC) 和交流 (AC) 的角度來考慮電源完整性,兩者一樣重要。PDN 中有多個積體電路可當作汲極,每個電路各自以不同的頻率開啟和關閉,這就是交流。去耦合電容器是儲存局部電荷,並將電流變化的影響降到最低的必要元件。

透過交流阻抗分析,您可確定將交流效應降到最低所需的去耦合電容器數量。由於電路板上空間有限,使用數量剛剛好的去耦合電容器,可節省製造成本。最佳的數位設計將使用最少的去耦合電容器,同時仍可確保絕佳的穩定度。

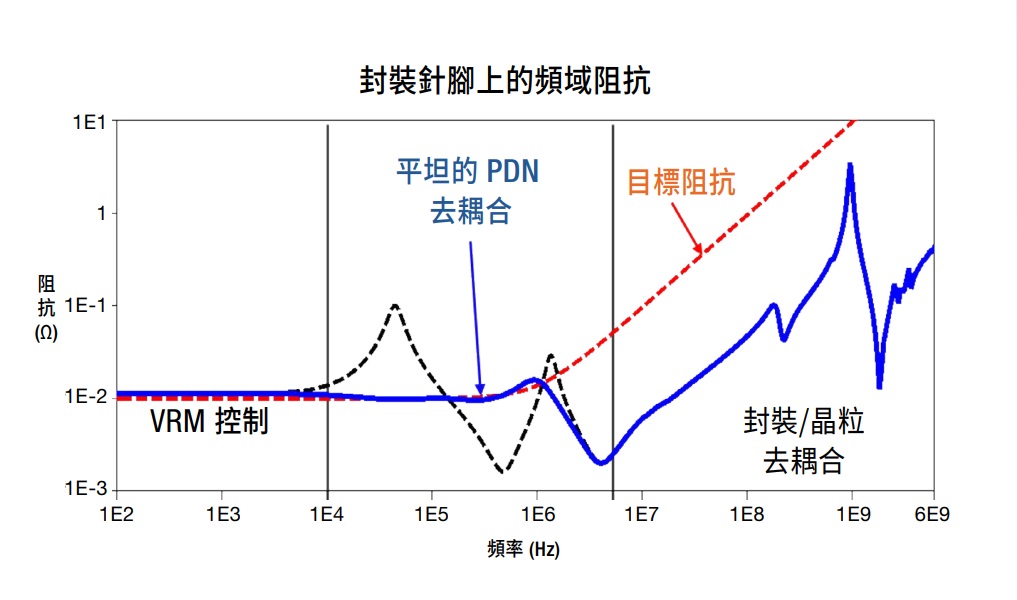

實現平坦的阻抗設計

過去,電源完整性工程師常使 用目標阻抗,來確定設計在特定頻率範圍內能獲得充足的電源。而目標阻抗是 PDN 的最高阻抗極限值。如果目標阻抗低於此極限值,則設計工程師可確定不會有電源完整性問題。

然而,對當今的高速數位電路板而言,光考慮目標阻抗是不夠的。您還須考慮會影響電路板的其他雜訊源。從直流到最高頻率元件,PDN 阻抗必須是平坦的,而且不能僅低於目標阻抗。為確保平坦的阻抗,您可在低頻時使用電源供應器的反饋迴路,在中頻和高頻時使用去耦合電容器。此外,您需採取「最佳阻尼」設計,以避免出現漣波,並針對大電流需求提供快速的趨穩時間。平坦阻抗法可同時因應這 2 項要求。

平坦阻抗最佳化

進行平坦阻抗最佳化時,您須使用最少的電容器來實現平坦阻抗,並同時避免可能導致異常電壓突波的高共振。減少電容器的數量,也有助於減少銲點的數量,進而提高可靠性。將阻抗最佳化後,您可改善效能、降低成本,並提高可靠性。

因此,完整的電源完整性工作流程應結合直流壓降和交流阻抗分析,以及平坦阻抗設計。藉由解決進行這些分析所發現的問題,您可支援從發電到負載供電的整個電源完整性生態系統。

設計人員必須在更小的空間中,納入更多的元件,以實現更高的效能。這使得功率密度不斷升高,並導致溫度大幅升高,對導體和電介質都會造成嚴重破壞。電壓或環境因素導致溫度升高,會影響設計的熱和電子特性,並造成更大的損耗、不穩定的系統性能,甚至導致裝置故障。

此外,過了一段時間,高溫還會帶來可靠性問題。在高溫循環下,導孔筒會變得容易脆裂。溫度升高是長期困擾 PCB 設計人員的一個因素,但當今高速數位 設計 電 路 板 的 要求, 已 遠 遠 超 過 傳 統 PCB 熱管 理 流 程 所能 處 理 的。消除高溫效應,對 PCB 效能和可靠性,甚至對重量、應用規模、成本和功率要求等,都有重大的影響。

在處理熱效應問題時,請先問自己 2 個問題:

1. 熱源在哪裡?

2. 高溫如何流向周圍環境?

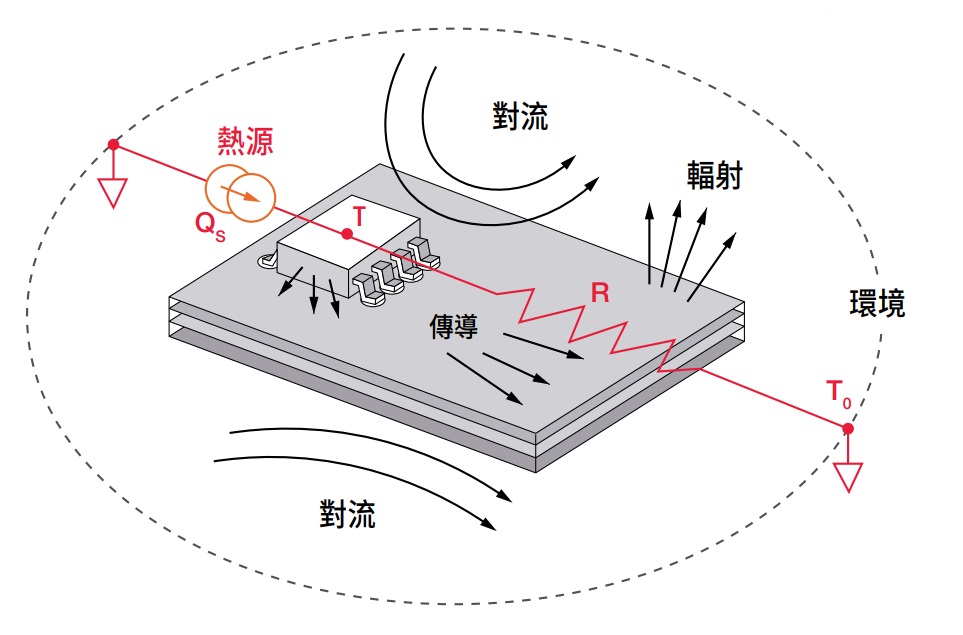

熱源在哪裡?

您可透過一種或多種機制進行散熱,包括輻射、對流和傳導。在決定以何種方式管理系統和元件的溫度時,請務必考慮這三點。

1. 輻射 – 透過電磁波傳播熱能

2. 對流 – 透過流體轉換熱能

3. 傳導 – 在 2 個直接接觸的物體之間傳遞熱能

哪個導孔的溫度較高?

我們很難判斷導孔是否過小,使得電流難以通過。而溫度是否上升,取決於與導孔相連的導線寬度,而導線的電阻,會隨溫度升高而增加,使得我們很難以手動計算方式來推估導孔的最終溫度。為此,在進行設計時,您必須針對所有熱效應進行模擬分析,以便確定最終導孔溫度。

測試您的假設 – 您覺得如何?

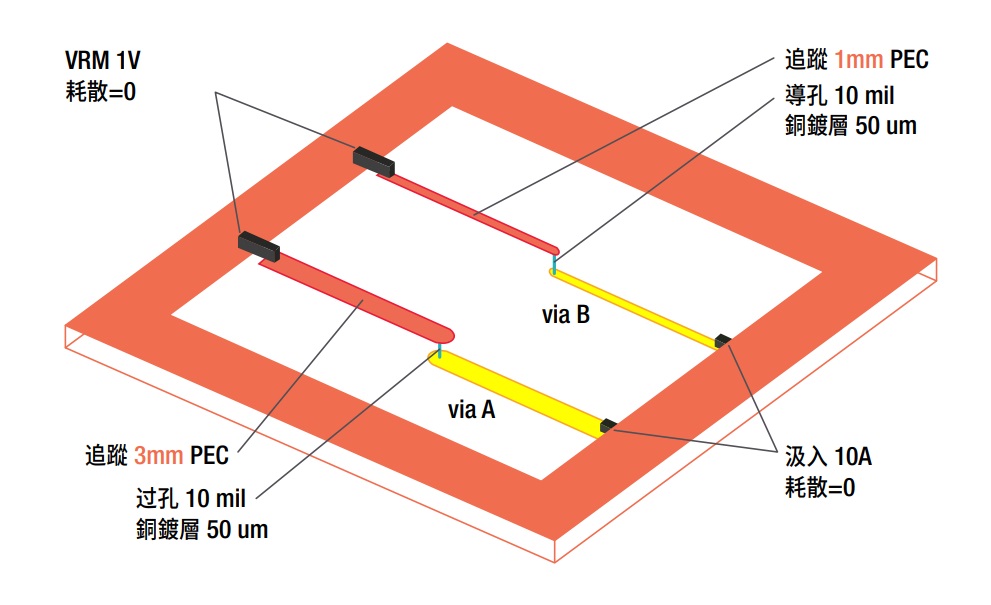

在相同環境條件下,以下 2 個相同的導孔,您覺得哪個導孔的溫度比較高?

• 導線寬度為 3 mm 的導孔 A

• 導線寬度為 1 mm 的導孔 B

導線對導孔溫度的影響有多大?

電熱分析可更準確地預測溫度

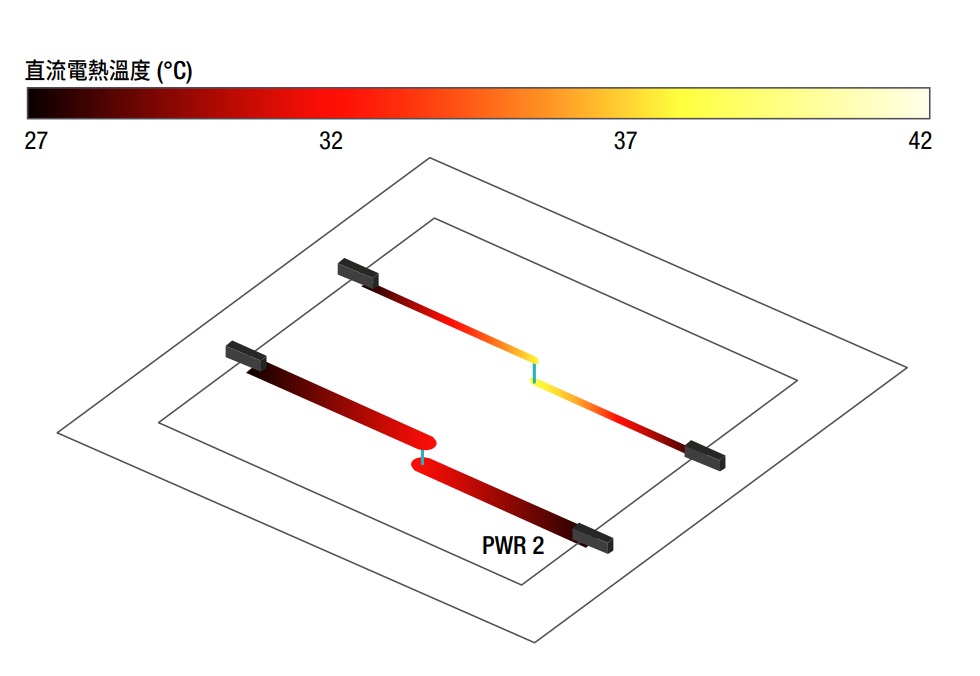

答案:導孔 B

導線寬度越窄,溫度越高。根據電熱分析結果,導孔 B 的溫度為 42 °C,導孔A 為 36 °C。

為什麼?

連接到導孔 A 的金屬導線線徑較寬,可提高散熱效率。但其實真正的原因很複雜。導線溫度每改變 10°C,電阻值就會改變 4%,導孔溫度也會隨之升高。因此您需使用電熱模擬器來計算溫度。

以下是個簡化的範例。在高速數位電路板上,熱散逸和傳遞是極複雜的過程。電路板的冷卻特性與許多因素息息相關,包括可用的金屬、材料特性、元件密度和放置位置、冷卻元件和環境條件等。所有這些因素是相互關聯的。電熱分析是唯一可準確預測熱效應並防止過熱的方法。

在創造新的顛覆性技術之前,您必須先克服各種艱鉅的技術挑戰。當暫態模擬(SPICE) 不再能夠滿足現代高速數位電路板的需求,通道模擬就成了最佳選擇。

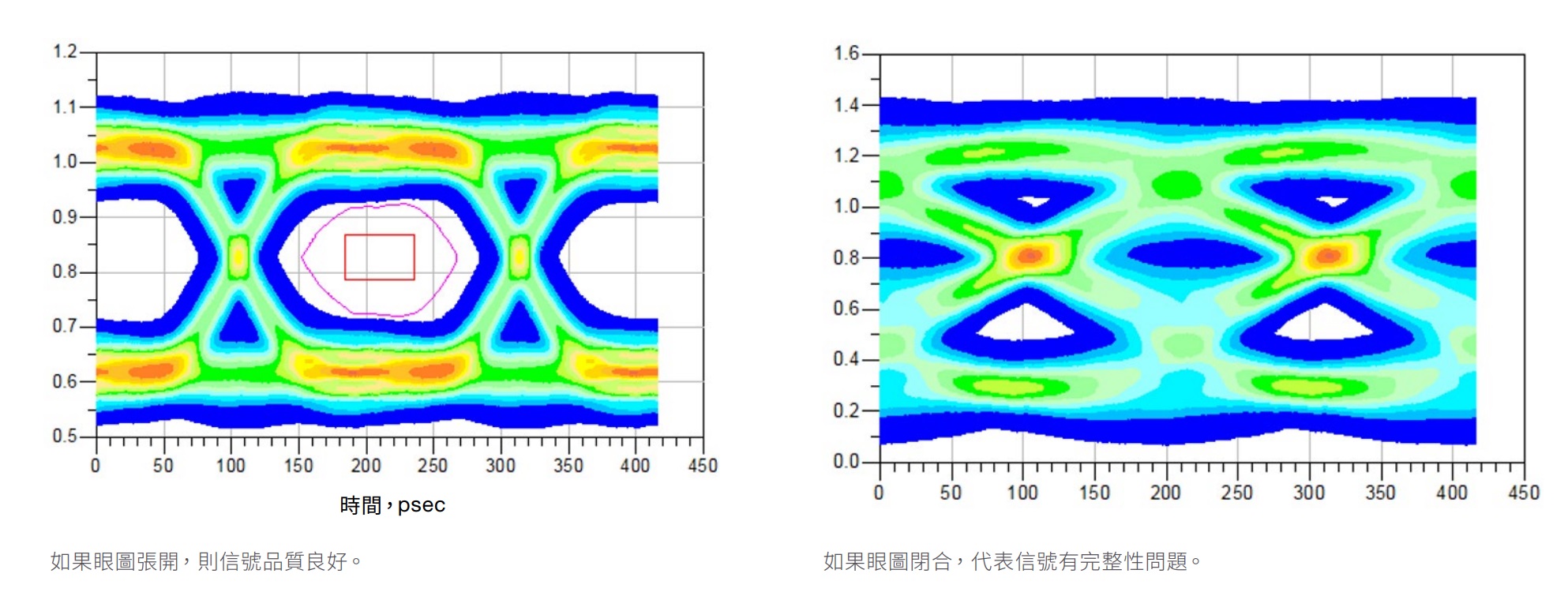

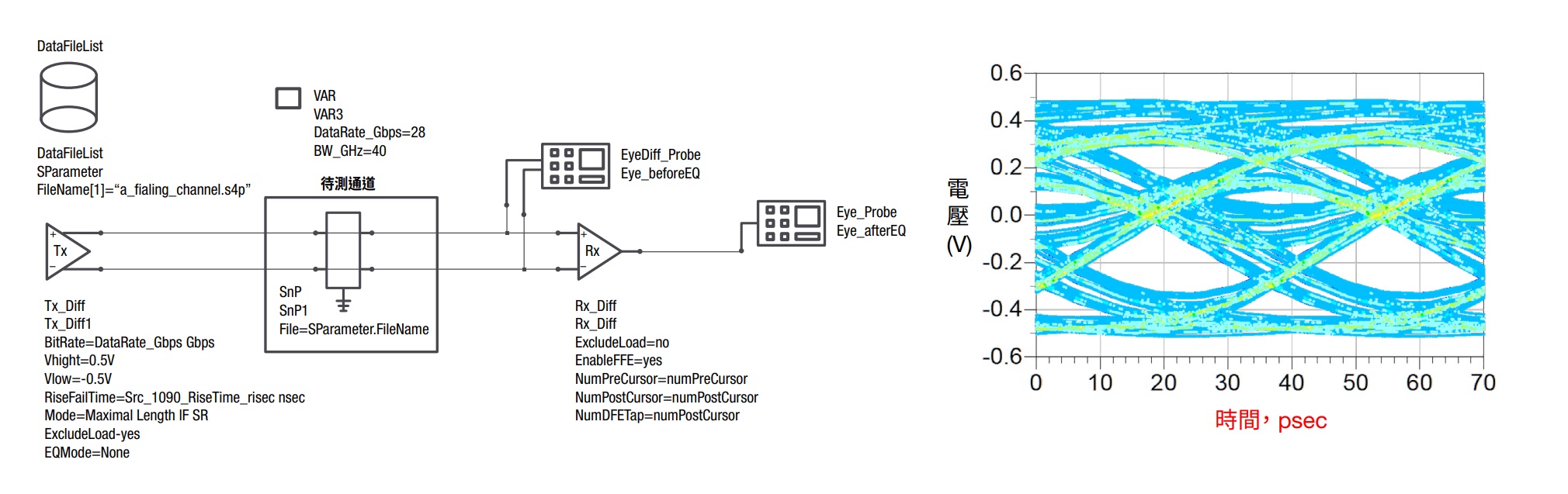

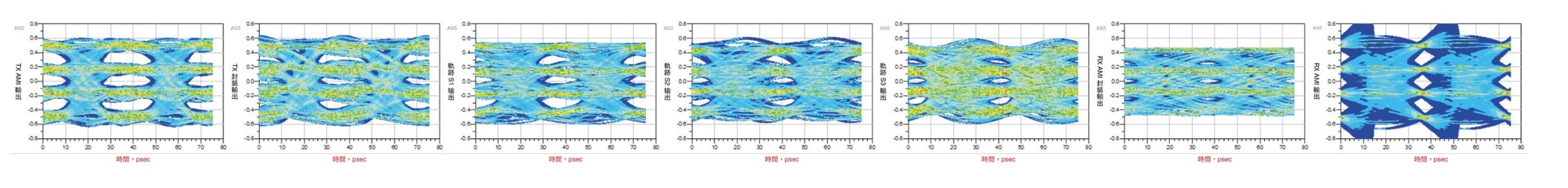

通 道模擬可快 速分析高速串列和並聯通訊 鏈 路中的通 道。在典型的情境中,通 道模擬器可在幾分鐘內處理 數百萬位元的碼型,以便準確分析眼圖特性,包括密度、寬度、高度、浴缸和誤碼率 (BER) 輪廓。通道模擬器還可針對符際干擾、隨機 抖動、串擾、編碼、等化,以 及高速 數位設計人 員 感興 趣的其他效應,進行模擬。

藉由執行通道模擬,您可確信您的高速數位電路板設計,將符合所有規格要求。如此一來,您可將複雜系統的 PCB 互連和等化功能最佳化。

需要進行通道模擬的 2 個應用

應用 1:400 gigabit 乙太網路

使用者對集中式資料互連網路的需求不斷升高,推動了乙太網路的技術突破與創新。400G 乙太網路便是最好的例子,它象徵著 PCB 電子介面的顛覆性技術突破。不歸零 (NRZ) 和四階脈衝振幅調變 (PAM4),是兩種可實現 400G 的調變技術。PAM4 雖可大幅提高資料傳輸速率,但卻非常容易受到雜訊的干擾,因為它們將 4 個信號位準打包成 2 個振幅擺盪。

您可透過 IBIS-AMI(輸入/輸出緩 衝區資訊規格演算法建模介面)模型,有效處理更高的資料傳輸速率。利用 IBIS-AMI 模型,您可準確地分析發射器和接收器的效能,並提供有助於實現可攜性、IP 保護、互通性和快速模擬的模型。如果您打算使用供應商提供的 IBIS-AMI 模型,那麼您一定要進行通 道模擬,否則您就無法準確地模擬具有抖動、等化、時脈和資料復原的複雜信號鏈路。藉由執行完整的通道模擬,您將因阻抗變化而產生的符際干擾降到最低,特別 是在電流通過導孔時。

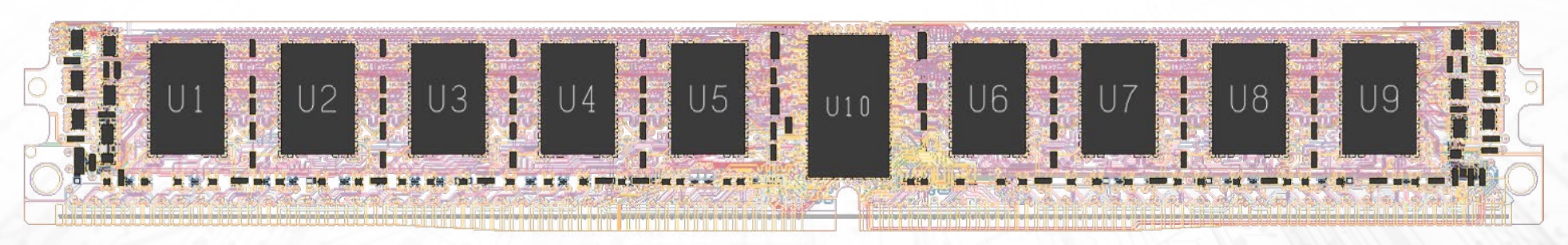

應用 2:雙倍資料速率記憶體

雙倍資料速率 (DDR) 記憶體的設計,一 代比一 代更複雜。與此同時,模擬和測試配置也日漸複雜,導致模擬與測試設定時間也隨之增加。如此一來,想要將模 擬和測試 資料進行關聯 性比 對 變 得更為困難,不但降 低了設計可信度,還延長了故障排除時間,最終錯過了最佳的產品上市時程。

負責設計記憶體系統的工程師,必須因應時序和電壓邊限不斷縮小的挑戰,並同時執行各種複雜的相符性量測,以確保產品能夠可靠地運作。最新的 DDR5和 LPDDR5 標準特別強調隨機抖動測試的重要性。設計人員必須確定他們的記憶體設計,能夠在超低 BER 下,通過接收器波罩測試。

通道模擬可提升您的自信度,讓您能針對 DDR5 及更高版本的設計複雜性進行建模。隨著邊限縮小,記憶體設計能夠容忍的誤差空間也越來越小。通道模擬可快速計算各種極端狀況。

結論

深入了解高速數位設計

高速數位設計的一項重大挑戰是,多個不同專業領域的工作流程最後必須串連在一起。本文分享的 4 個考量,已成為整體高速 數位設計的一部分。但 如果沒有一個可將不同工程師的結果串連在一起的工作流程,他們很難有效地將高速數位設計最佳化。是德科技的整合式設計和模擬軟體提供高速數位工作流程,可實現快速、準確且最佳化的設計。

不論您選擇以何種方式進行高速數位設計,有一點非常顯而易見。使用正確的設計工具,並利用本電子書提出的 4 個考量,來有效進行整體設計,可以讓您快速邁向成功之道。

立即下載 [是德電子書- 成功實現高速數位設計的 4 個考量]

延伸閱讀相關應用文章:

• 高效能電源技術(PDN)設計線上論壇

• 執行最佳電源完整性量測

• 如何確定示波器之信號完整性

• 評估示波器的取樣率 VS. 取樣實度

高速數位標準正迅速發展,以因應 5G、物聯網、人工智慧、虛擬實境,以及自動駕駛汽車等新興技術,對高速資料傳輸的需求。每一代高速運算標準的更迭,都帶來新的信令功能、更快的資料傳輸速率,以及更小的設計邊限。然而,隨著速度大幅提升,工程師卻面臨著新的設計挑戰。因此,您需要準確度更高的模擬、新的軟體工具,以及更有效率的工作流程。

身為硬體工程師,您的工作是設計、驗證、製造和測試電子產品。在產業趨勢急速變化的今天,您必須採用全新的設計方法,以解決印刷電路板 (PCB) 高速信號品質下降,甚至於產品故障的問題。其後果可能是專案延遲、預算超支,或商譽嚴重受損等風險。

想要避免這種進退兩難的局面,就需要新的設計工具,以及可連接多個專業領域的全方位設計方法。如此一來,您可根據各種不同的介面標準進行設計,但設計和驗證時間不會因而延長。請閱讀此電子書,了解成功實現完整高速數位設計的 4 個重要考量。

考量 1:信號完整性問題會導致效能下滑

信號完整性(象徵電子信號的品質)與我們身邊所有事物息息相關。在數位通訊通道中,信號完整性分析是指,對穿過 PCB 導線、導孔、連接器和其他元 件的電子 信號 進 行 研究。信號 完 整 性問 題會 對數位設計造 成 嚴 重破 壞,包括效能減損、良率下降,甚至是現場故障情形。我們通常一直到設計和測試週期的後期,才會發現這些代價高昂的問題。

模擬 PCB 信號完整性的最佳時間點,是布局後、製造前。隨著數位設計的速度不斷提高,進行完整的模擬變得越來越重要。而且現在有更多因素,會導致信號完整性問題。經常出現的問題包括:互連裝置的反射(阻抗不匹配)、導線之間的電磁耦合,以及接地問題等。這些問題如不加以解決,可能會導致信號失真和衰減。

從長遠效益來看,進行信號完整性分析和模擬,可減少後期設計失敗的風險,並可協助您將設計邊限最大化,進而節省時間和金錢。

了解實現數位通道信號完整性的 3 個步驟

理想狀況下,從繪製電路圖,到電路板通過最終測試的每個環節,您都應該將信號完整性納入考量。藉由以模擬方式測試您的創新設計,是驗證通道信號完整性的最佳方法。為此,請遵循以下 3 個步驟:

第 1 步:使用眼圖來模擬通道

信號會從發射器穿過 PCB 傳送到接收器。在傳播過程中,導線、連接器和纜線都會產生干擾,信號的振幅和時序將因而惡化。透過眼圖,您可確認信號到達接收器時的品質。

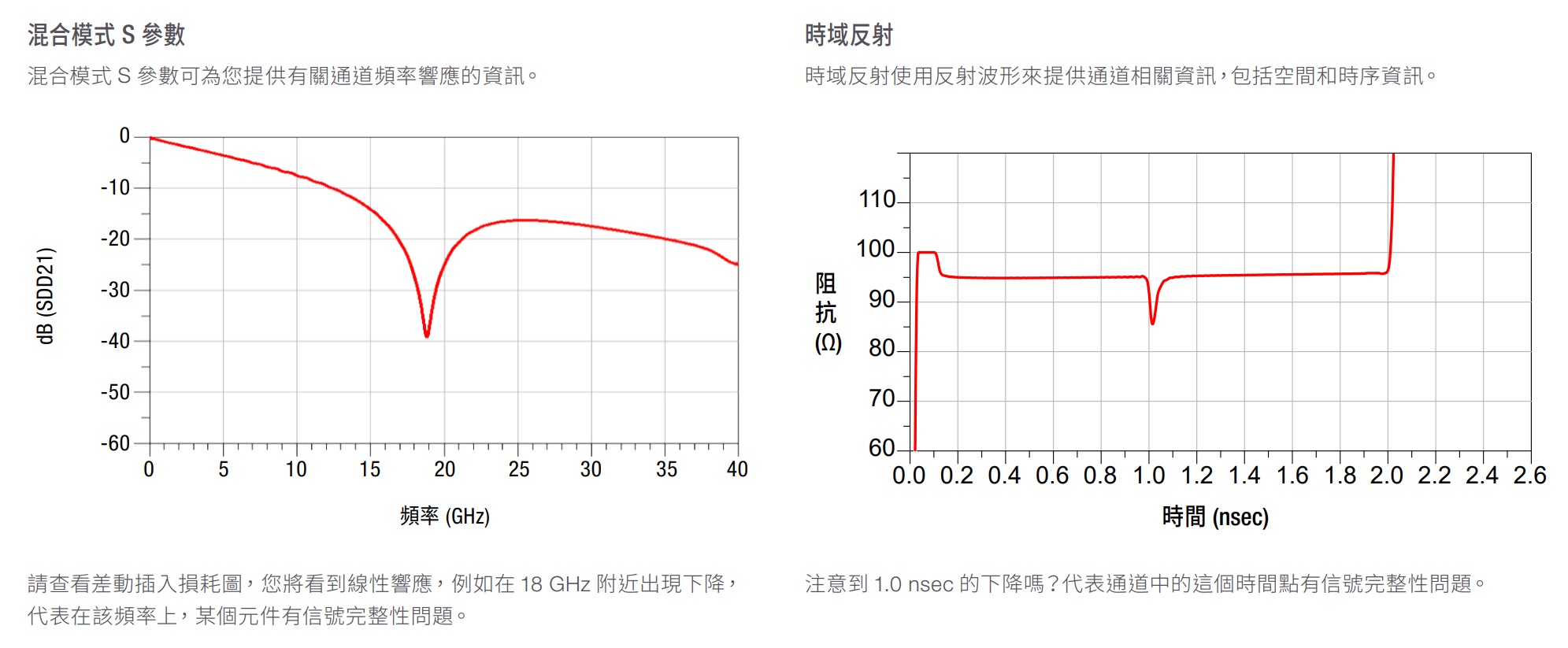

第 2 步:找到導致信號品質惡化的問題根源

發現信號完整性問題後,您可透過 2 項主要分析,來確定數位設計的問題根源。

第 3 步:解決設計問題

找出導致信號完整性問題的根源後,您需考慮可針對設計進行哪些修改。

一個常見的問題根源是導孔殘段的長度。導孔可在多個 PCB 層之間提供電子連接,而導孔殘段是連接器中用不到的部分,會導致信號品質顯著下降。進行背鑽(back drilling,亦即使 用鑽頭去除不需要的殘段)有助於大幅改善信號完整性。完成設計修正後,請務必再次模擬通道,確保您的眼圖是張開的。

考量 2:及早預測電源完整性是成功關鍵

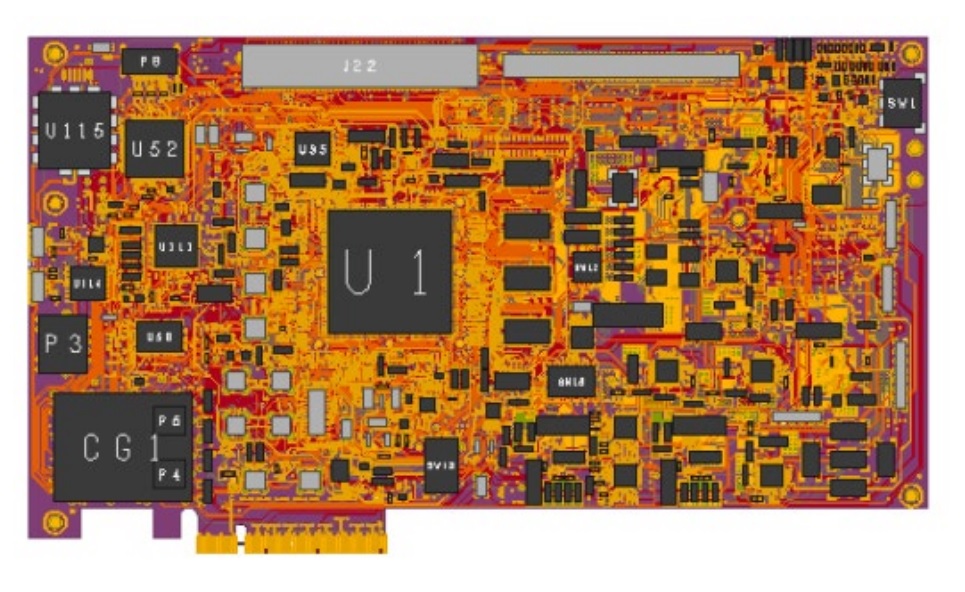

如果等到完成產品設計,才發現無法通過相符性測試,您將付出高昂的代價。首先,藉由新增濾波器和電容器來修改設計,會提高製造成本。而且重新設計還會拖延產品上市時間,導致營收下滑。在設計階段儘早了解並減輕潛在的電源問題,可以讓您贏在起跑點。進行電源完整性分析的目的是,確保電路板上的驅動器和接收器,都能獲得正常運作所需的電壓和電流。為確保電源完整性,您需避免設計出現直流壓降(電流流經電源層與接地層的電阻時所出現的電壓損耗)。

早期了解設計細節至關重要

以下 3 項要求,使得電源完整性挑戰變得更嚴苛,並提高了出現直流壓降的機率。

1. 更高的元件整合度 – 更高的整合度有助於實現更密集的布線,進而提高電源網路的電流密度,但同時也會造成更大的直流壓降。

2. 更低的電源電壓 – 1 V 的 10% 容差度,要比 1.2 V 的 10% 容差度更嚴格,因此會出現更大的壓降。

3. 更小的外觀尺寸 – 隨著 PCB 尺寸變小, 可容納更寬電源平面的空間也變得更小, 進而導致直流壓降。

您不能等到完成布局後,再來執行電源完整性分析。因此,早期了解設計細節,是在高速數位電路板上成功供電的關鍵。

有助於了解電源完整性的 2 項關鍵分析

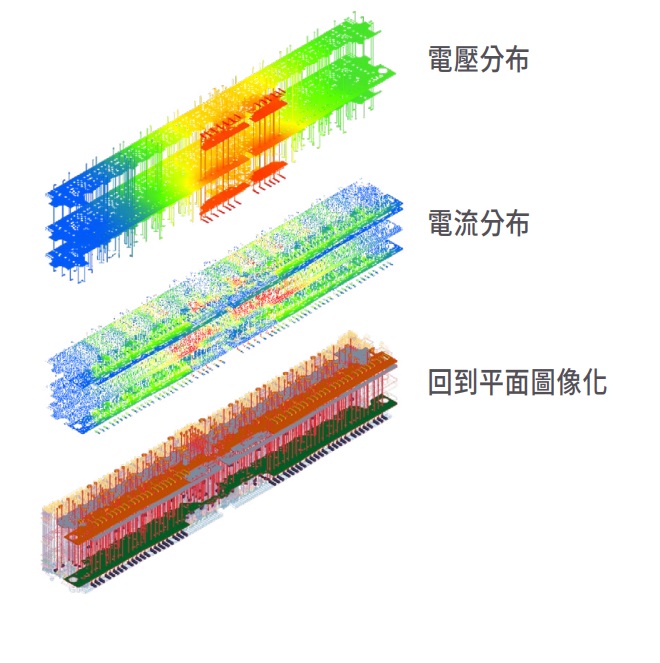

早期模擬和分析,有助於確保電路板的電源完整性。請務必將這 2 項分析,視為整體高速數位設計流程的一部分。

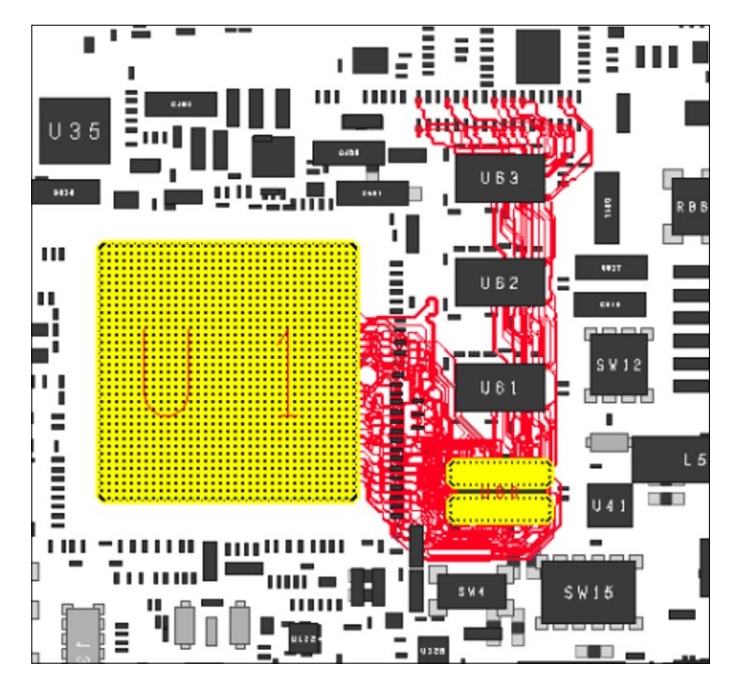

分析 1:直流壓降

在整個 PCB 上分配電源時,如果 壓降過 大,則負載 端之電 壓可能無法因應必要元件規格的要求。直流壓降分析可確保 PCB 導線和平面,能夠符合電源供應器的要求。

而且這項分析功能,可顯示選定之電源網路和接地網路的電壓分布狀態。您還可利用此分析來檢視電流密度,以了解如何全面改善您的設計。請務必查看電源供應器穩壓器模組及其導孔的位置。此外,您需考慮電流被迫流經導孔周圍孔洞 (void) 之狹窄路徑的問題。

分析 2:交流阻抗

您必須同時從直流 (DC) 和交流 (AC) 的角度來考慮電源完整性,兩者一樣重要。PDN 中有多個積體電路可當作汲極,每個電路各自以不同的頻率開啟和關閉,這就是交流。去耦合電容器是儲存局部電荷,並將電流變化的影響降到最低的必要元件。

透過交流阻抗分析,您可確定將交流效應降到最低所需的去耦合電容器數量。由於電路板上空間有限,使用數量剛剛好的去耦合電容器,可節省製造成本。最佳的數位設計將使用最少的去耦合電容器,同時仍可確保絕佳的穩定度。

實現平坦的阻抗設計

過去,電源完整性工程師常使 用目標阻抗,來確定設計在特定頻率範圍內能獲得充足的電源。而目標阻抗是 PDN 的最高阻抗極限值。如果目標阻抗低於此極限值,則設計工程師可確定不會有電源完整性問題。

然而,對當今的高速數位電路板而言,光考慮目標阻抗是不夠的。您還須考慮會影響電路板的其他雜訊源。從直流到最高頻率元件,PDN 阻抗必須是平坦的,而且不能僅低於目標阻抗。為確保平坦的阻抗,您可在低頻時使用電源供應器的反饋迴路,在中頻和高頻時使用去耦合電容器。此外,您需採取「最佳阻尼」設計,以避免出現漣波,並針對大電流需求提供快速的趨穩時間。平坦阻抗法可同時因應這 2 項要求。

平坦阻抗最佳化

進行平坦阻抗最佳化時,您須使用最少的電容器來實現平坦阻抗,並同時避免可能導致異常電壓突波的高共振。減少電容器的數量,也有助於減少銲點的數量,進而提高可靠性。將阻抗最佳化後,您可改善效能、降低成本,並提高可靠性。

因此,完整的電源完整性工作流程應結合直流壓降和交流阻抗分析,以及平坦阻抗設計。藉由解決進行這些分析所發現的問題,您可支援從發電到負載供電的整個電源完整性生態系統。

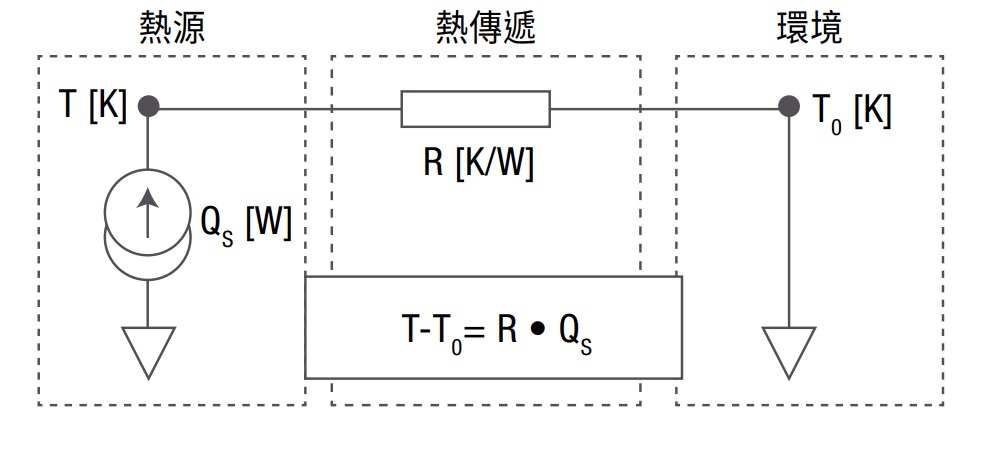

考量 3:熱效應

電路板變得越來越熱設計人員必須在更小的空間中,納入更多的元件,以實現更高的效能。這使得功率密度不斷升高,並導致溫度大幅升高,對導體和電介質都會造成嚴重破壞。電壓或環境因素導致溫度升高,會影響設計的熱和電子特性,並造成更大的損耗、不穩定的系統性能,甚至導致裝置故障。

此外,過了一段時間,高溫還會帶來可靠性問題。在高溫循環下,導孔筒會變得容易脆裂。溫度升高是長期困擾 PCB 設計人員的一個因素,但當今高速數位 設計 電 路 板 的 要求, 已 遠 遠 超 過 傳 統 PCB 熱管 理 流 程 所能 處 理 的。消除高溫效應,對 PCB 效能和可靠性,甚至對重量、應用規模、成本和功率要求等,都有重大的影響。

在處理熱效應問題時,請先問自己 2 個問題:

1. 熱源在哪裡?

2. 高溫如何流向周圍環境?

熱源在哪裡?

您可透過一種或多種機制進行散熱,包括輻射、對流和傳導。在決定以何種方式管理系統和元件的溫度時,請務必考慮這三點。

1. 輻射 – 透過電磁波傳播熱能

2. 對流 – 透過流體轉換熱能

3. 傳導 – 在 2 個直接接觸的物體之間傳遞熱能

哪個導孔的溫度較高?

我們很難判斷導孔是否過小,使得電流難以通過。而溫度是否上升,取決於與導孔相連的導線寬度,而導線的電阻,會隨溫度升高而增加,使得我們很難以手動計算方式來推估導孔的最終溫度。為此,在進行設計時,您必須針對所有熱效應進行模擬分析,以便確定最終導孔溫度。

測試您的假設 – 您覺得如何?

在相同環境條件下,以下 2 個相同的導孔,您覺得哪個導孔的溫度比較高?

• 導線寬度為 3 mm 的導孔 A

• 導線寬度為 1 mm 的導孔 B

導線對導孔溫度的影響有多大?

電熱分析可更準確地預測溫度

答案:導孔 B

導線寬度越窄,溫度越高。根據電熱分析結果,導孔 B 的溫度為 42 °C,導孔A 為 36 °C。

為什麼?

連接到導孔 A 的金屬導線線徑較寬,可提高散熱效率。但其實真正的原因很複雜。導線溫度每改變 10°C,電阻值就會改變 4%,導孔溫度也會隨之升高。因此您需使用電熱模擬器來計算溫度。

以下是個簡化的範例。在高速數位電路板上,熱散逸和傳遞是極複雜的過程。電路板的冷卻特性與許多因素息息相關,包括可用的金屬、材料特性、元件密度和放置位置、冷卻元件和環境條件等。所有這些因素是相互關聯的。電熱分析是唯一可準確預測熱效應並防止過熱的方法。

考量 4:系統分析

透過通道模擬提高設計自信度在創造新的顛覆性技術之前,您必須先克服各種艱鉅的技術挑戰。當暫態模擬(SPICE) 不再能夠滿足現代高速數位電路板的需求,通道模擬就成了最佳選擇。

通 道模擬可快 速分析高速串列和並聯通訊 鏈 路中的通 道。在典型的情境中,通 道模擬器可在幾分鐘內處理 數百萬位元的碼型,以便準確分析眼圖特性,包括密度、寬度、高度、浴缸和誤碼率 (BER) 輪廓。通道模擬器還可針對符際干擾、隨機 抖動、串擾、編碼、等化,以 及高速 數位設計人 員 感興 趣的其他效應,進行模擬。

藉由執行通道模擬,您可確信您的高速數位電路板設計,將符合所有規格要求。如此一來,您可將複雜系統的 PCB 互連和等化功能最佳化。

需要進行通道模擬的 2 個應用

應用 1:400 gigabit 乙太網路

使用者對集中式資料互連網路的需求不斷升高,推動了乙太網路的技術突破與創新。400G 乙太網路便是最好的例子,它象徵著 PCB 電子介面的顛覆性技術突破。不歸零 (NRZ) 和四階脈衝振幅調變 (PAM4),是兩種可實現 400G 的調變技術。PAM4 雖可大幅提高資料傳輸速率,但卻非常容易受到雜訊的干擾,因為它們將 4 個信號位準打包成 2 個振幅擺盪。

您可透過 IBIS-AMI(輸入/輸出緩 衝區資訊規格演算法建模介面)模型,有效處理更高的資料傳輸速率。利用 IBIS-AMI 模型,您可準確地分析發射器和接收器的效能,並提供有助於實現可攜性、IP 保護、互通性和快速模擬的模型。如果您打算使用供應商提供的 IBIS-AMI 模型,那麼您一定要進行通 道模擬,否則您就無法準確地模擬具有抖動、等化、時脈和資料復原的複雜信號鏈路。藉由執行完整的通道模擬,您將因阻抗變化而產生的符際干擾降到最低,特別 是在電流通過導孔時。

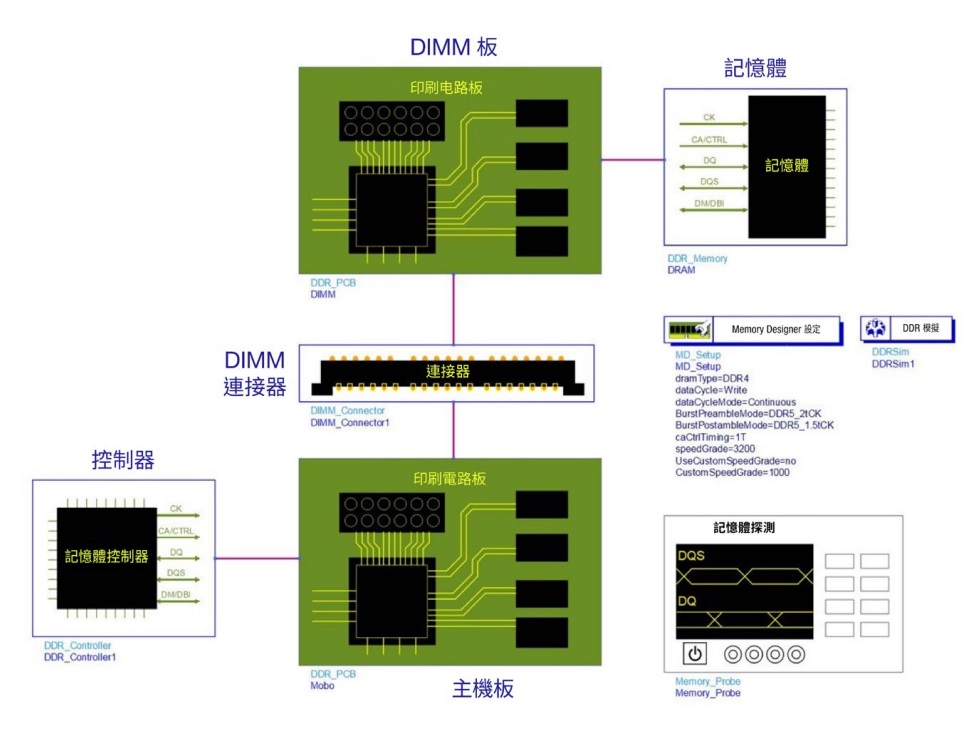

應用 2:雙倍資料速率記憶體

雙倍資料速率 (DDR) 記憶體的設計,一 代比一 代更複雜。與此同時,模擬和測試配置也日漸複雜,導致模擬與測試設定時間也隨之增加。如此一來,想要將模 擬和測試 資料進行關聯 性比 對 變 得更為困難,不但降 低了設計可信度,還延長了故障排除時間,最終錯過了最佳的產品上市時程。

負責設計記憶體系統的工程師,必須因應時序和電壓邊限不斷縮小的挑戰,並同時執行各種複雜的相符性量測,以確保產品能夠可靠地運作。最新的 DDR5和 LPDDR5 標準特別強調隨機抖動測試的重要性。設計人員必須確定他們的記憶體設計,能夠在超低 BER 下,通過接收器波罩測試。

通道模擬可提升您的自信度,讓您能針對 DDR5 及更高版本的設計複雜性進行建模。隨著邊限縮小,記憶體設計能夠容忍的誤差空間也越來越小。通道模擬可快速計算各種極端狀況。

結論

深入了解高速數位設計

高速數位設計的一項重大挑戰是,多個不同專業領域的工作流程最後必須串連在一起。本文分享的 4 個考量,已成為整體高速 數位設計的一部分。但 如果沒有一個可將不同工程師的結果串連在一起的工作流程,他們很難有效地將高速數位設計最佳化。是德科技的整合式設計和模擬軟體提供高速數位工作流程,可實現快速、準確且最佳化的設計。

不論您選擇以何種方式進行高速數位設計,有一點非常顯而易見。使用正確的設計工具,並利用本電子書提出的 4 個考量,來有效進行整體設計,可以讓您快速邁向成功之道。

立即下載 [是德電子書- 成功實現高速數位設計的 4 個考量]

延伸閱讀相關應用文章:

• 高效能電源技術(PDN)設計線上論壇

• 執行最佳電源完整性量測

• 如何確定示波器之信號完整性

• 評估示波器的取樣率 VS. 取樣實度